来源:内容由半导体行业观察(ID:icbank)编译自idtechex,谢谢。

2024-2034年,2.5D、3D、先进半导体封装、RDL、介电材料、Cu-Cu混合键合、EMC、MUF等,先进的半导体封装为有机介电材料提供了巨大的市场机会。

为什么我们需要先进半导体封装?

我们生活在一个以数据为中心的世界。各行业产生的数据量不断增长,日益推动对高带宽计算的需求。机器学习和人工智能等应用需要强大的处理能力,因此需要在芯片上密集放置晶体管,并在封装中采用紧凑的互连凸点间距。后者强调了半导体技术在满足这些要求方面的重要性。

半导体封装已从板级集成发展到晶圆级集成,带来了显着的进步。晶圆级集成具有优于传统方法的优势,例如增加的连接密度、更小的尺寸敏感应用的占地面积以及增强的性能。

“先进”半导体封装具体包括高密度扇出、2.5D 和 3D 封装,其特点是凸点间距尺寸低于 100 µm,可实现至少 10 倍的互连密度。

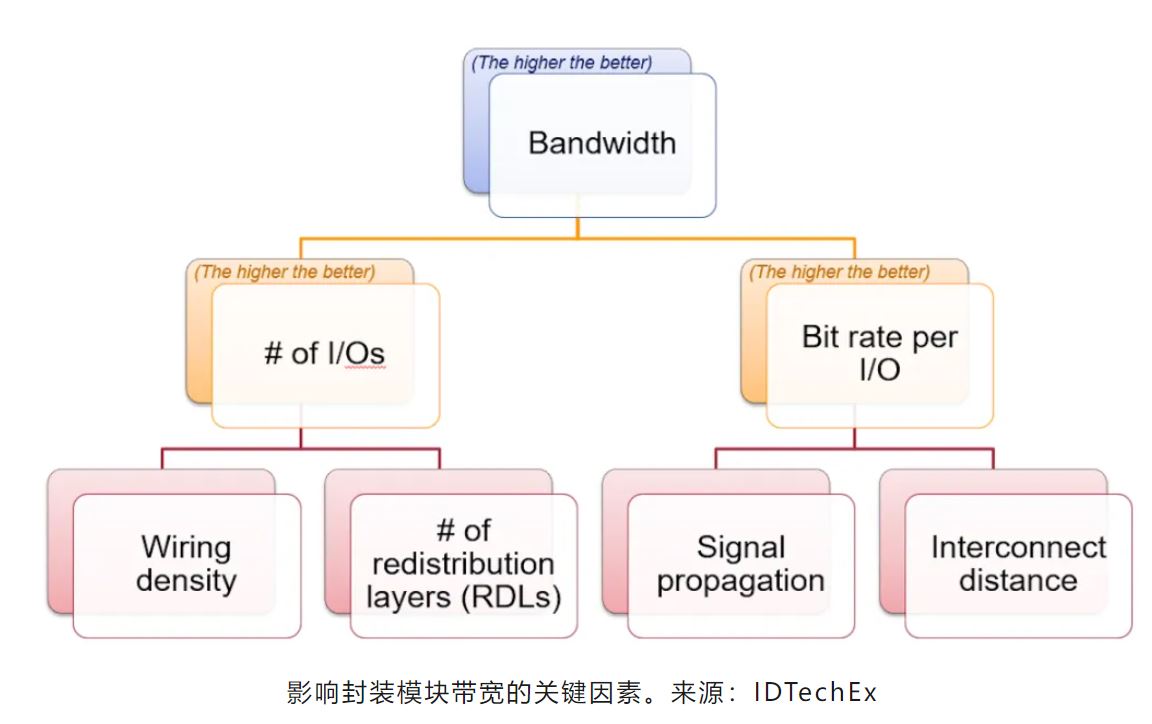

带宽是关键

为了从封装的角度增强带宽,两个关键因素发挥作用:I/O(输入/输出)总数和每个 I/O 的比特率。增加 I/O 总数需要在每个布线层/再分配层 (RDL) 中启用更精细的线路/空间 (L/S) 图案,并具有更多数量的布线层。另一方面,提高每个 I/O 的比特率受到小芯片之间的互连距离和电介质材料选择的影响。这些因素直接影响包装系统的整体性能和效率。

释放高带宽:探索先进半导体封装的材料和工艺

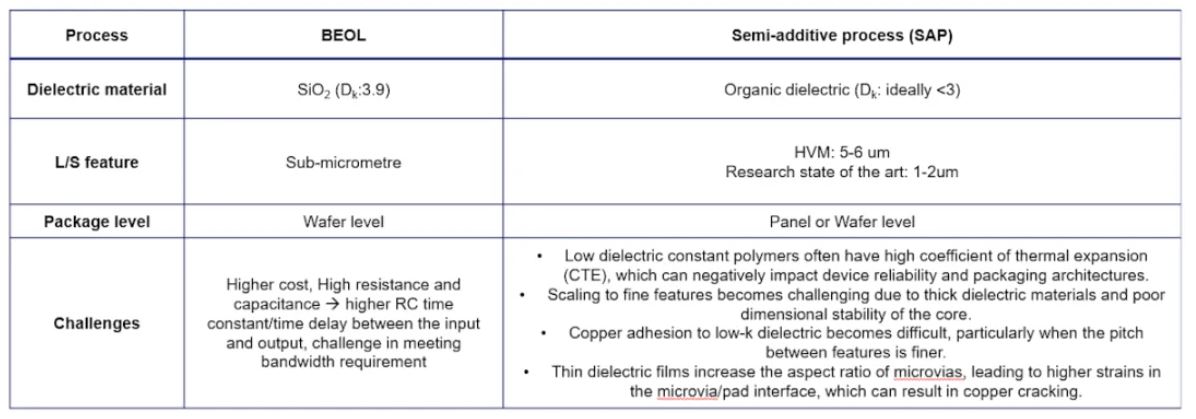

从材料和加工的角度深入研究实现更高的布线密度和更高的每个 I/O 比特率,揭示了介电材料的选择和适当的加工技术的利用所发挥的关键作用。这些因素对包装系统的整体性能和功能具有重大影响。

电子互连:SiO2与有机电介质。来源:IDTechEx

选择合适的介电材料至关重要,要考虑低介电常数、最佳 CTE(尽可能接近铜的 CTE)等特性以及确保模块可靠性的有利机械特性(例如杨氏模量和伸长率)。这些选择可实现更高的数据速率,同时保持信号完整性并促进细线/空间功能以增加布线密度。

在 GPU 等高性能加速器中,SiO2 等无机电介质已被广泛用于实现超细线/空间 (L/S) 特性。然而,由于其高 RC 延迟,它们在需要高速连接的应用中的使用受到限制。作为替代方案,有机电介质因其成本效益和通过其低介电常数减轻 RC 延迟的能力而被提出。然而,有机电介质面临着挑战,包括高 CTE(这会对器件可靠性产生负面影响)以及难以缩放到精细 L/S 特征。

除了选择合适的材料外,封装制造过程中采用的处理技术对于实现更多 I/O 数量和提高每个 I/O 的比特率也起着至关重要的作用。 2.5D 封装工艺涉及的步骤,包括光刻、CMP(化学机械平坦化)、蚀刻工艺以及 3D Cu-Cu 混合键合中的 CMP 和键合工艺,对实现更紧密的布线和增加布线密度提出了挑战。

英文原文